パルスジェネレータ

■製作のきっかけ

「作りながら学ぶエレクトロニクス測定器」(本多平八郎著、CQ出版社)は、 発振器、電源、ユニバーサルアンプなどアナログ回路の評価に必要なツールを作り、 作りながらアナログ回路を学んでいく本です。

回路図があり、回路の解説をしているだけという本ではなく、仕様の検討から回路設計、SPICEシミュレーション、製作に使用する部品の解説、実際に製作された基板の写真も含めた実装の解説、完成したツールの評価まで全て解説されていて、配線やケース加工のノウハウまで載っています。これがこの本の凄いところです。

実際に自分で回路を作りながら回路を学び、自分で作ったツールを使ってまた新しい回路を作ることができたら、きっと大きな満足感があると思います。

この本を読んで、まずはパルスジェネレータから作ることにしました。 パルスジェネレータは、製作したアンプの評価などにも使えそうです。

このパルスジェネレータは、0.2Hz〜10MHzのクロック出力、その反転出力、最小パルス幅100ns,分解能8ビットのパルスパターン出力2チャンネルを備えています。 ロータリーDIPスイッチでクロック周期を設定すれば、その周期のクロックと反転クロックが出力されます。 また、8bitのDIPスイッチが2つついており、出力するパルスパターンを設定します。

■CPLDを使う

「作りながら学ぶエレクトロニクス測定器」(以下、参考書)で紹介されている回路は、74シリーズで分周回路、パターン発生回路を構成していますが、配線するのが面倒なのでCPLDで作ることにしました。CPLDを使うことで部品点数が減り、配線も少なくなります。

CPLDに書き込む回路は、分周回路、パルス発生回路です。 パルス発生回路の出力にハザード防止のFFを入れていること以外、参考書の回路と同じ回路構成です。ハザードを防止するためには、ジョンソンカウンタを使ってもいいかと思います。

CPLDはXilinxのXC9572を使いました。XC9536では、マクロブロック数が足りません。 電源回路、発振回路、ドライバ回路は参考書の回路と同じです。

PCBEを使って基板パターン設計を行いました。「出力されるものは周波数の低いデジタルのパルス」と高をくくって製作したせいで、ただ線をつないだだけのパターンになっています。このことが後で大きなあだとなったのでした...

■製作、完成のはずが

土日でチャチャッと作って完成! とする予定だったのですが、出力波形を見てみると、汚い! パターン出力Aでパルスを出しておいて、パターン出力BをLレベルに設定すると、AのスイッチングノイズがBにも出てきます。両方Hレベルに設定しても、ぴったり5Vが出力されず、ノイズが載っています。

確かにデジタル回路としての機能は十分に満たしているのだが、このパルスジェネレータに接続するのはアナログ回路。これでは満足できません。

内部の様子

自作のターミネーター(左:直列終端、 右:並列終端) 参考書参照

■不良原因調査

電源ラインをオシロで観測してみると、200mVp-pくらいのノイズが載っていて、どうやら電源がおかしいらしい。レギュレータはいつもの3端子レギュレータではなく、シャントレギュレータとTrで構成されていて、しかもTrは参考書の回路で使われている2SC1226ではなく、手持ちの2SD526を使っている。電源回路が発振しているのではないか?

ICを全部外してみると、発振が止まる。負荷がなくなったせいなのか? 電源回路のエミッタフォロワが発振しているのか? ベースに抵抗を入れてみたり、出力のコンデンサを増やしたりするが、全く変化がない。この電源は、一体いくつの周波数で発振しているのか? もしかして、電源の問題ではなく、電源ラインにスイッチングノイズが乗っているのか?

わからないことが多いと、原因の絞り込みもできず、もうお手上げ状態で3ヶ月経ちました。

→結局、原因はオシロのプローブのGNDリードがノイズを拾っているだけでした。 詳しくは、オシロのプローブのGNDリード

■一応完成?

電源回路も問題なく動作していることがわかりました。

出力波形が汚い原因の1つは、ドライバ(74AC540)1つで2chの出力を駆動しているため、片方のスイッチングノイズが 他方のチャンネルに出てきてしまうことです。

これは、IC内部の電源インピーダンスが高いためなので、チャンネル毎に74AC540を使わなければ解決できないでしょう。

もう1つは、基板の電源ラインのインピーダンスが高いために、片方のドライバーのスイッチングノイズが他方のドライバに流れてしまうことです。 下は、パルス出力が常にLになるよう設定し、クロック出力とパルス出力を見たときの波形です。

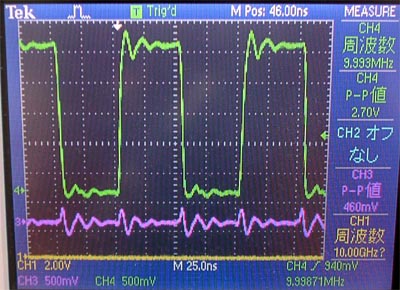

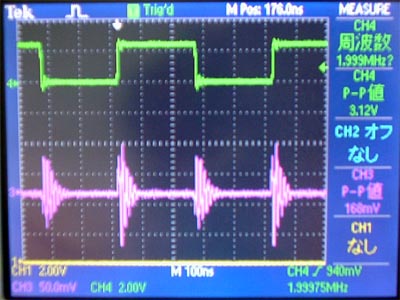

クロック出力(緑 )、パルス出力(ピンク)クロック出力のドライバのスイッチングするたびに、ノイズが電源ラインに乗り、パルス出力のドライバに流れ込んでいるのです。 対策として、ドライバ周りの電源配線を太くすること、電源配線をドライバ毎に分け、ドライバに入る前にLを入れて他のドライバへノイズが流れ込まないように するなどすれば解決するかもしれません。 DIPパッケージで電源ピンとGNDピンが対角にあるICを使っていることも問題だと思います。

もし、作り直すとすれば、両面基板にして、電源パターンを太くとって、出力ドライバもFETなどできちんと作りたいと思います。 とりあえず、使えるようになったので、改良したいところはあるものの、今回はこれで完成ということにしました。 それにしても、いろいろと問題を考えることの多い回路でした。